비아(Via)란?

Top Layer와 Bottom layer를 연결해 주는 통로 역할을 하며, 노이즈제거, ESD 쉴드, GND보강, 열분산 등 많은 역할을 한다.

JLCPCB Via 설정들에 대한 설명

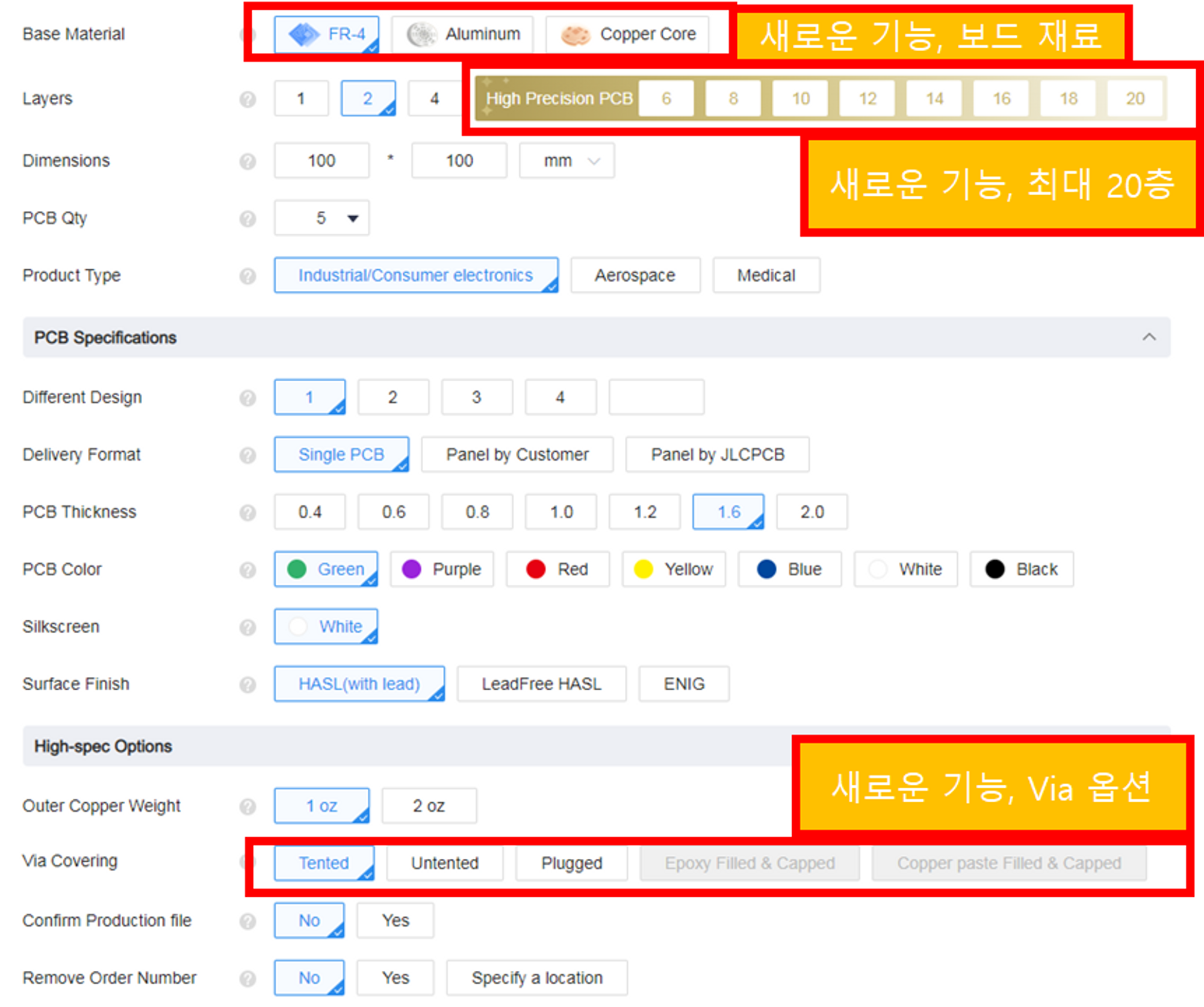

보드 제작하려고 JLCPCB.com 에 접속했다. 최근 업데이트로 여러 옵션들이 생겼다. 전세계를 대상으로 하는 사업을 확장하면서 캐파는 키울만치 키웠고, 이제 품질에 대한 선택, 즉 옵션을 소비자에게 제공함으로써 다양한 가격 정책을 통해 마진을 높이려는 사업전략이라고 생각된다.

오늘은 새로생긴 옵션들은 많지만 그 중 **비아(Via)**에 대한 설명을 준비했다.

내용을 시작하기전, 기본 용어로 솔더마스크에 대해서 알고 다음내용을 읽으면 이해가 쉽다. 솔더마스크는 솔더마스킹 잉크가 덮이는 것을말한다. 솔더마스크가 된 납이 뭍지 않도록 초록 잉크로 덮힌 Via가 있고, Via위에 바로 도금 위에 납땜이 가능한 Via 가 있다. 즉 솔더마스크가 된 Via는 납땜이 안되도록 잉크로 가려진 부분이다.

솔더마스크(Soldermask)란?

- 보통 PCB보드의 전체적으로 덮혀있는 마스크(보통 초록색, 또는 다양한색) 을 말함

- 납땜을 할 때 납이 패드에만 잘 머무를 수 있도록 도와주는 마스크

- 특정 곳에 납이 잘 뭍게 하지 않으려면 아래와 같은 솔더 레지스트를 바르는 방법도 있음

JLCPCB Via 옵션 다섯가지

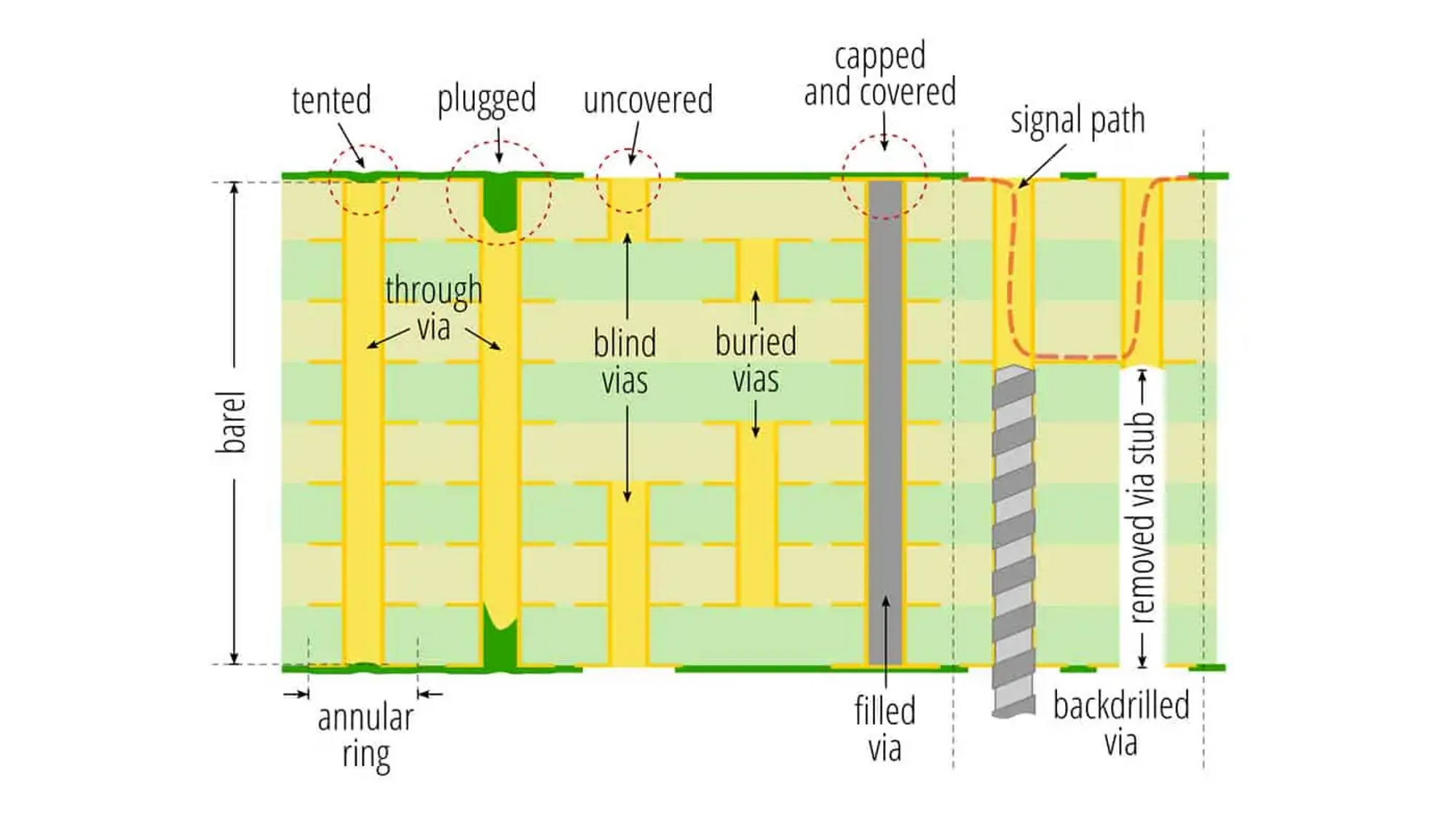

비아의 옵션에는 다섯가지 종류가 있다. 요약하면 다음과 같다.

- Tented

- PCB 공정에서 솔더마스크 잉크를 밀때 잉크가 via를 통과

- 경험상 via직경이 0.4mm 이하이면 via가 덮히는 형태

- 0.5mm 이상이면 via구멍안으로 잉크가 흐러내릴 수 있고, 주변부 패드가 노출(partially tented) 됨

- Untented

- PCB 공정에서 솔더마스크 잉크를 밀때 잉크가 via를 통과하지 않음

- uncovered 그림과 같이 via주변 솔더마스크 잉크 없이 via가 노출됨

- via 홀에 바로 납땜이 가능

- Plugged

- PCB 공정 중 HPL(Hole Plugging Land)공정이 추가된 via형태.

- 솔더마스크 잉크를 한번더 via홀에 충전시켜서 보다 확실하게 via구멍을 막음

- via의 도금이 노출되는 것을 방지

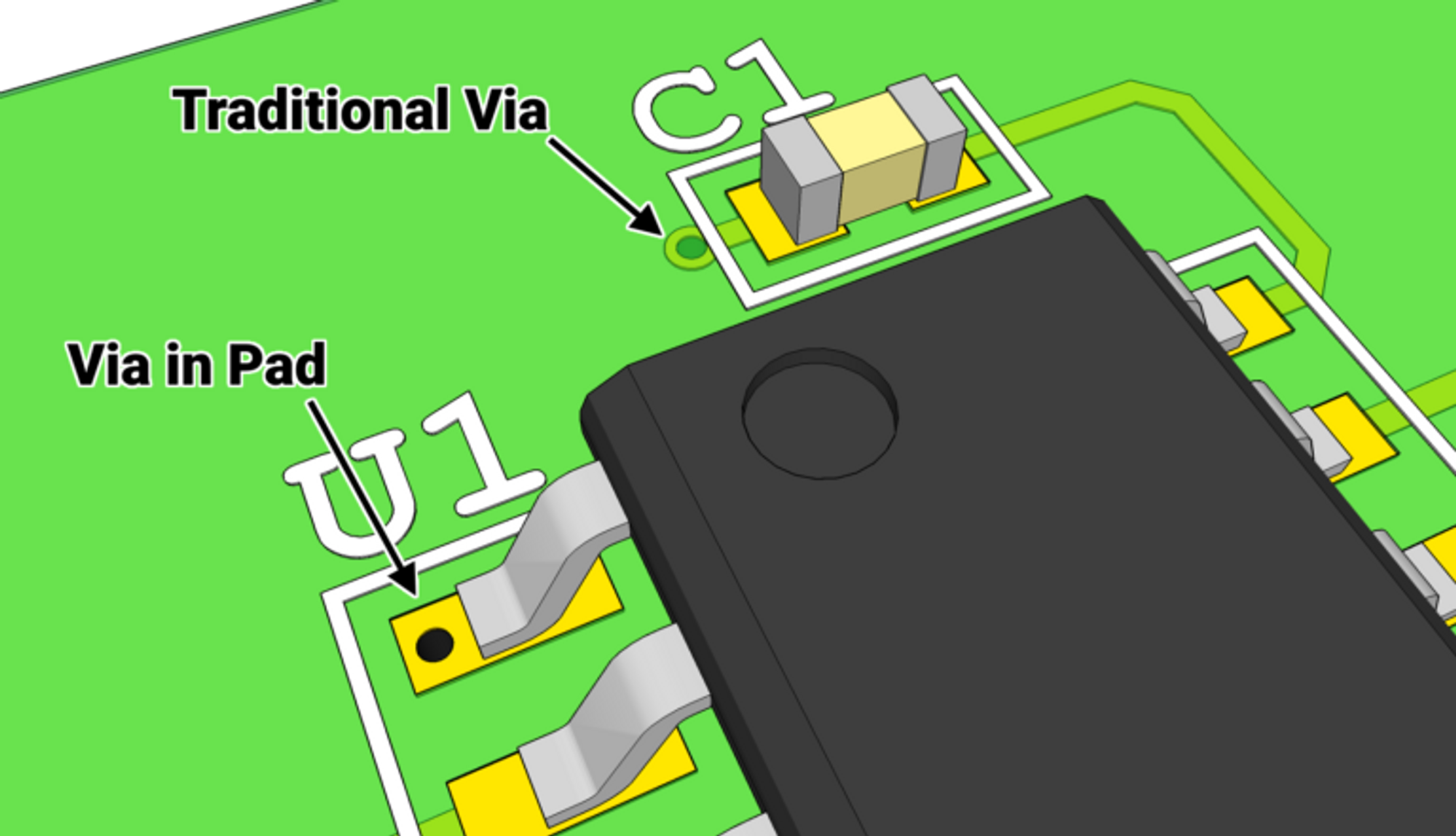

- Epoxy filled & Capped

- via홀 내부에 에폭시로 절연 충전재를 채우고 구리 도금하여 평평하고 납땜가능한 형태

- 4층기판 이상에서부터 옵션선택 가능

- via in pad 및 두꺼운 보드에 적용하는 편

- Copper paste filled & Capped

- via홀 내부에 구리충전재로 채워지고, 평평하고 납땜가능한 형태로 표면이 도금됨

- 4층기판 이상에서부터 옵션선택 가능

- via in pad 및 높은열전도율로 인한 히트 싱크패드에 이상적

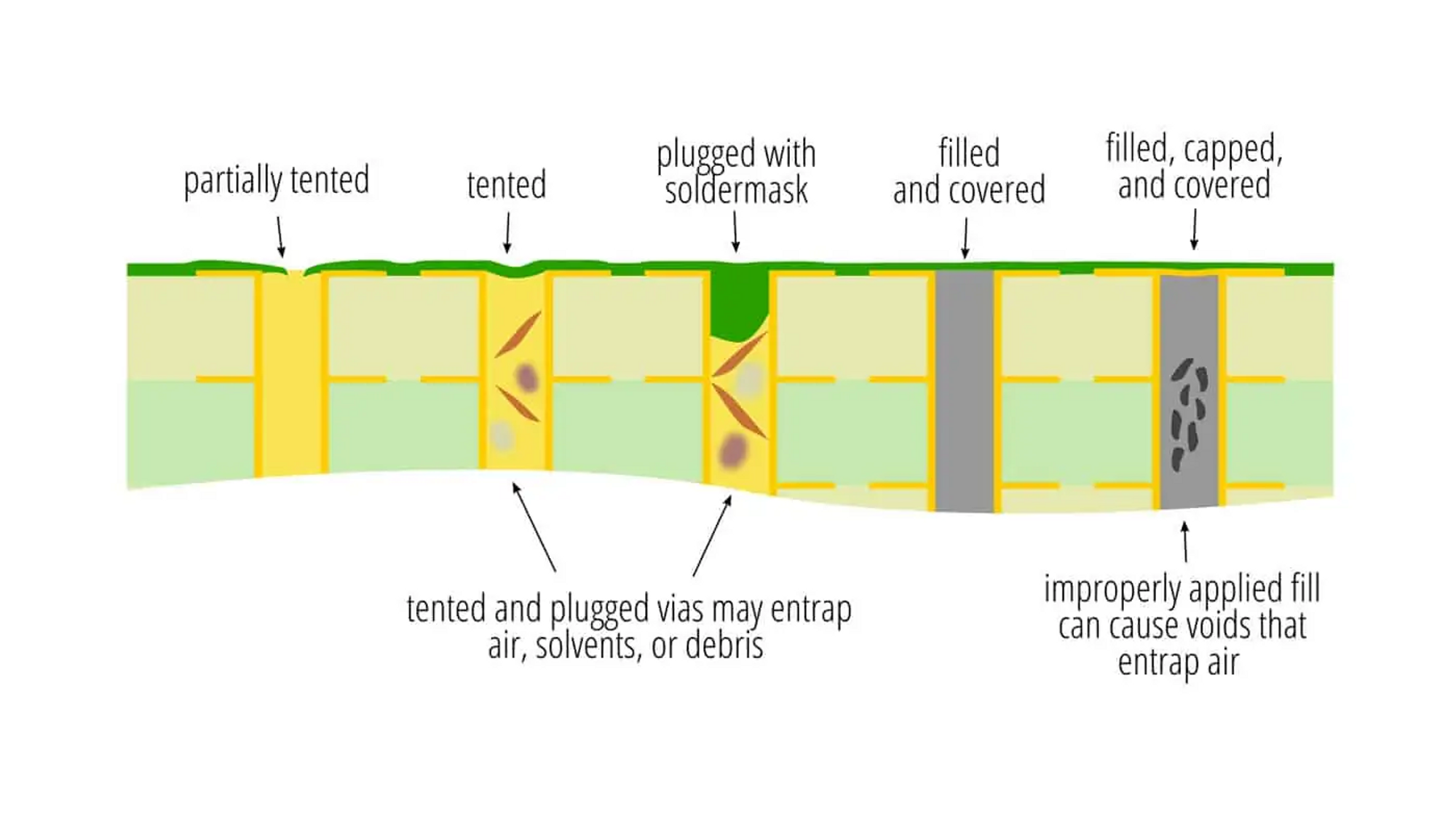

1. Tented 기본형

Vias are covered with soldermask and are not processed with HASL or ENIG. Boards with 6+ layers are upgraded to Epoxy Filled & Capped Via for free. ”비아는 솔더마스크로 덮여 있고, HASL 또는 ENIG로 처리되지 않는다. 6층 레이어가 있는 보드는 에폭시 충전 & 캡드 비아로 무료로 업그레이드 된다.”

용어가 어려운게 두가지가 나왔다. 살펴보면

- HASL(Hot Air Solder Leveling) 금도금처리에 비해 제조하기 쉽고 저렴하다. PCB의 패드를 납으로 도포한 것을 말한다. PCB는 패드가 납과같은 은색이다.

- ENIG(Electroless Nikel Immersion Gold, 금도금) 처리를 한 PCB는 금색이다. 공정이 많아 시간이 걸리는 단점이 있다. 금도금이 니켈층을 보호하기에 보관성이 용이하다.이방법의 장점은 제조 공정이 간단하기 때문에, 1)추가적인 가공비가 없고 2)작업시간이 짧다.

- 단점 또한 있는데, via홀의 크기가 크다면, 솔더마스크가 via홀 안쪽으로 흘러내려서, via홀 주변부 도금이 노출될 수 있다. 개인적인 경험상 0.4mm 직경의 via는 왠만하면 간섭없게 사용할 수 있다.

- 즉, Via 안 쪽이 비어있고, 비아 가장 상단과 하단을 커버만하는기법이다.

2. Untented 노출형

Soldermask is removed over the via and its annular ring. The via will be solderable and has the same surface finish as regular pads. ”via와 via홀 주변 도금에서 솔더마스크가 없는 via이다. 이 via는 납땜이 가능하며, 일반 패드와 동일한 표면 마감을 한다.”

장점

- via가 어디로 뚫리고 어디로 나오는지를 찍어볼 수 있다는 것이다. 도통 시험으로 각 via의 출입을 쉽게 알수 있다는 장점이 있다.

단점

- 단점은 SMT공정에서 수삽할경우(손으로 납땜작업) 이 via에 원치않는 납이 뭍어 주변 via와 브릿지를 형성하는 경우가 생길 수 있다. 전원라인과 GND라인의 쇼츠라도 난다면 보드가 망가지게 된다.

업그레이드 해준다는 것은 에폭시 충전 비아와 캡드비아는 좀 더 좋은 비아일 것이다.

그렇다면 “좋은 비아란?” 무엇일까?

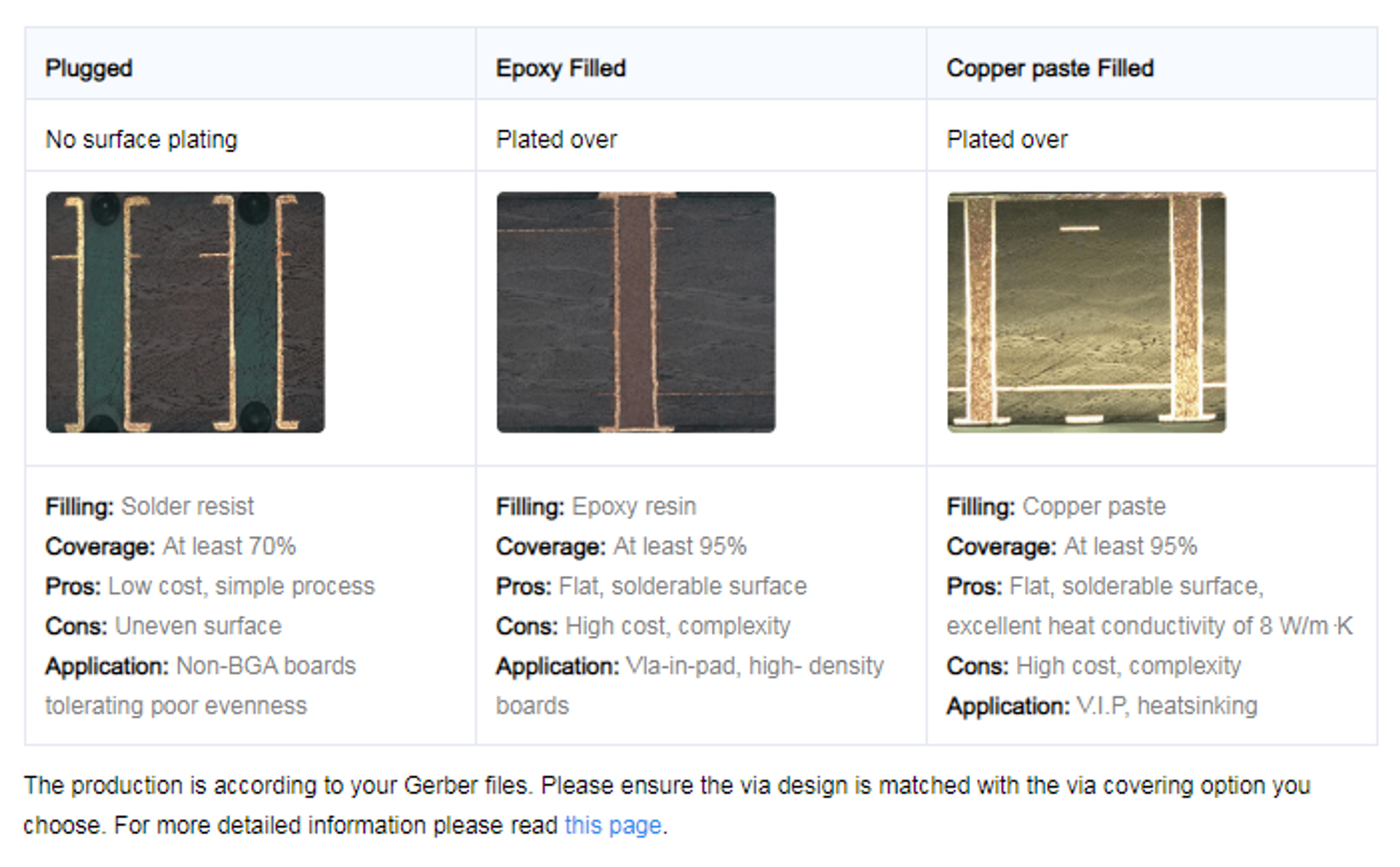

3. Plugged 충전재형

공정을 추가하여 via홀에 PSR잉크를 한번더 넣어서 도금부분이 외부로 노출되지 않도록 하는 via이다.

- 공정중 via홀 안쪽으로 공기층이 형성되거나 PCB위에 잔존 물질이 들어갈 수 있다.

- via홀에 PSR잉크를 넣는 공정이 추가되기에 추가비용을 받을 수 있다.

4. Epoxy filled & Capped

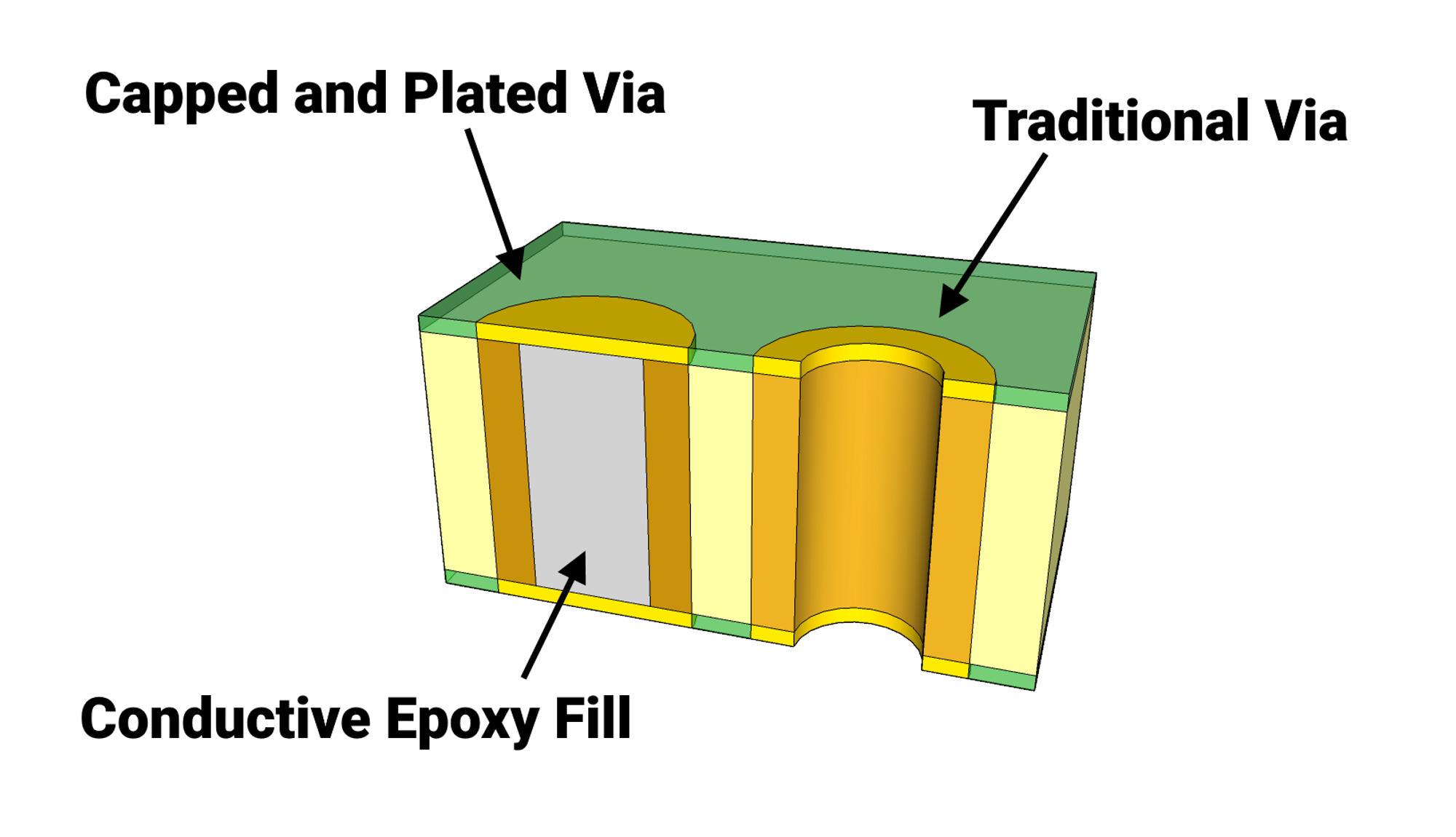

Epoxy filled & Capped via는 via홀(스루홀)이 차지하는 공간을 SMD조립 지점으로 사용하여 PCB의 상호 연결 밀도를 높이는 목적으로 사용된다. Traditional Via는 아래 사진과 같이. via홀 안쪽으로 드릴구멍이 뚫려있고, 내측벽은 도금되어있는 형태이다. 이에 반해 Epoxy filled & Capped via는 안쪽 구멍이 절연 충전재로 채워져있으며, via의 상단부와 하단부가 평평한 도금으로 Capped(뚜껑처럼) 막혀있다.

- 절연 충전 수지의 절연 특성과 온도에따른 치수변화가 상대적으로 중요하기 때문에 열처리한 다음 평탄화작업을하고 구리층으로 덮는 형태이다.

- via를 패드위에 올릴 수 있어서 PCB를 소형화 하는데 적합하다.

- 이 기술은 다양한 유형의 PCB를 제작하는데 사용할 수 있고 uBGA에 주로 사용되는 기술이다.

- 발열이 많이나는 부품에 발열을 낮추기위해 사용되기도 한다.

5. Copper paste filled & Capped

- 4번과 거의 동일한 공정을 거치지만, 내부 충전제가 절연체(에폭시)가 아닌 구리페이스트가 들어간다.

- 열전도율이 높은 구리페이스트 충전재는 8W/m-K의 우수한 열전도율을 가지고 있다.

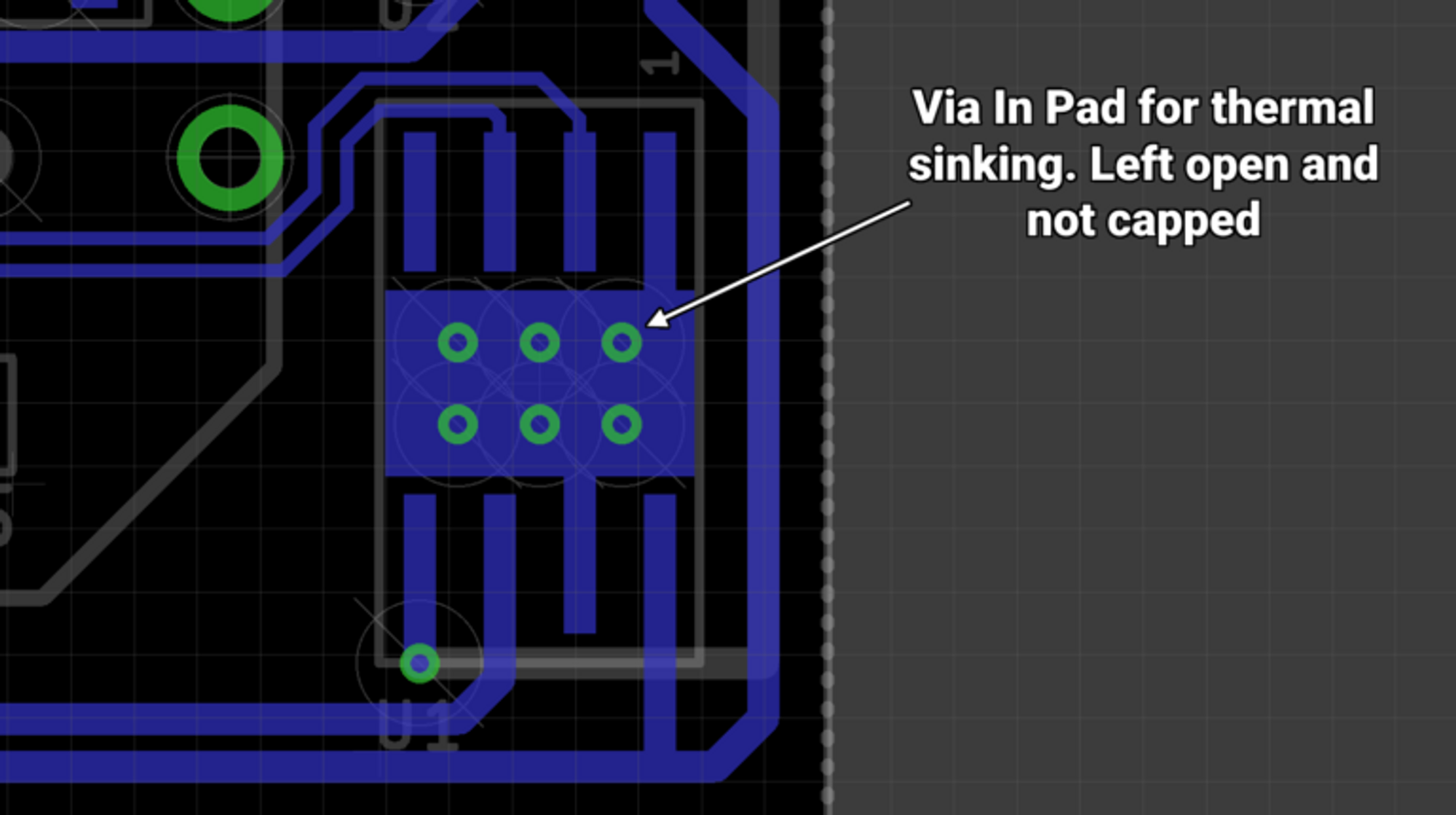

- via in pad가 가능하며, 히트싱크를 제작하는데 이상적인 via 이다.

5번을 쓰고나서 서멀비아에 대해서도 찾아보았다.

서멀 비아는 기판을 이용한 표면 실장 부품의 방열 효과를 향상시킨다.

구조적으로는 기판을 관통하는 구멍 (Hole)을 만들고, 1층의 양면 기판일 경우 기판 표면과 이면의 동박을 연결하여 방열에 이용하는 면적과 체적을 늘려 열 저항을 낮추는 방법이다. 다층 기판의 경우, 여러 층간의 면을 연결하거나, 부분적으로 연결하는 층을 한정짓는 방법이 있지만, 원리는 동일하다.

표면 실장 부품은 PCB (기판)에 실장함으로써, 열 저항을 낮추는 것을 전제로 하고 있다. 열 저항은 방열기의 역할을 하는 PCB 상의 동박 면적이나 두께, 또는 기판 두께나 재질에 의존한다. 기본적으로 넓고 두껍게 하여, 전달되기 쉽도록 함으로써, 방열 효과를 향상시킨다. 그러나, 동박의 두께는 일반적으로 표준 사양을 따르고 있으므로, 무턱대고 두껍게 할 수 없다. 또한, 소형화가 기본 사항으로 요구되고 있으므로, PCB의 면적을 원하는 만큼 취할 수도 없다. 실제로는 동박의 두께도 결코 두껍다고 할 수 없으므로, 일정 면적을 초과하게 되면 면적에 적합한 방열 효과를 얻을 수 없게 된다.

이러한 과제의 대응책 중 하나가 서멀 비아이다. 서멀 비아를 효과적으로 사용하기 위해서는, 서멀 비아를 발열체에 가깝게, 예를 들어 부품의 바로 밑에 배치하는 것이 중요하다.

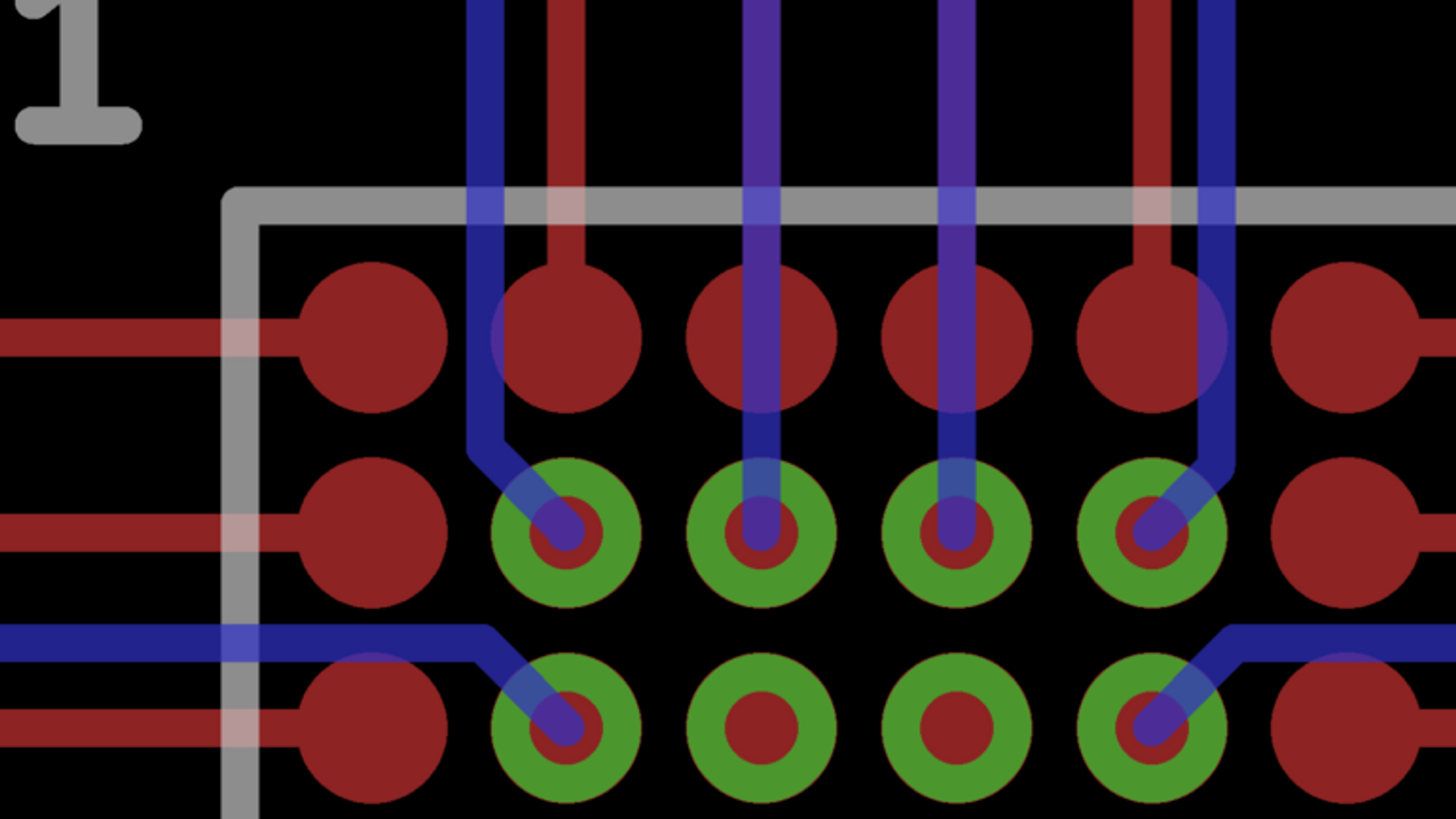

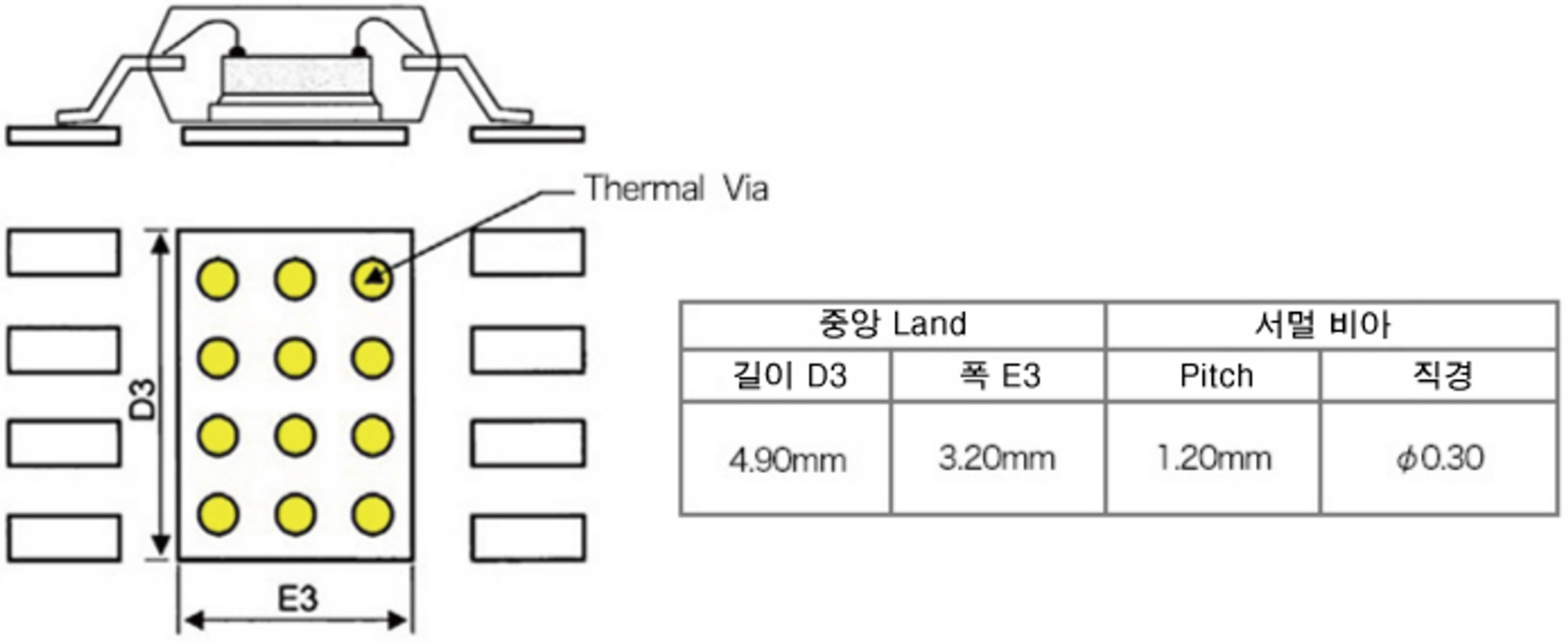

서멀 비아의 배치

구체적인 레이아웃 예로, 하기 그림은 이면에 방열판이 노출되어 있는 타입의 패키지 HTSOP-J8의 서멀 비아 레이아웃과 치수의 예입멀 비아는 열 전도율을 높이기 위해, 도금 충전 가능한 내경 0.3mm 정도의 작은 비아를 권장한다. Hole의 직경이 너무 크면 리플로 솔더링 (reflow soldering) 공정에서 솔더 유입 문제가 발생할 가능성이 있으므로 주의가 필요하다.

서멀 비아는 1.2mm 정도의 간격으로 패키지의 이면 방열판 바로 밑에 배치한다. 만약, 이면 방열판의 바로 밑에 배치한 것만으로 방열이 부족한 경우에는, IC 주변에도 서멀 비아를 배치한다. 이러한 경우, 되도록 IC에 가깝게 배치하는 것이 중요하다.

서멀 비아의 배치 및 사이즈 등에 대해서는, 각 회사에 따라 노하우가 있거나, 규칙으로 정해져 있는 경우가 있을 것이다. 이러한 경우에는, 상기 내용을 참조하여 더욱 큰 효과를 얻을 수 있도록 검토하기 바란다.

결론

오늘은 JLCPCB.com 에 새로추가된 via 홀 옵션에 대해 알아보았다. 다양한 via 옵션을 제작하는 PCB의 특성에 맞추어 옵션해보아야겠다. 자료를 찾아보던중 다양한 PCB의 종류에 대해서 알게되었다. 하이브리드 PCB 등과 같이 flexible과 rigid 한 특성을 모두 가지고 있는 PCB제작하는 특수 업체 등도 관심이 생겼다. 다음에는 PCB의 종류에 대해서 글을 작성해보겠다.

JLCPCB 는 저렴한가격에 SMT도 진행하며, 다양한 물성의 3D프린팅 샘플도 제공하기 때문에 제작자 입장에서는 저렴한가격에 좋은 품질의 반제품을 납품 받을 수 있어서 좋은 기업인 것같다.

'임베디드 용어설명' 카테고리의 다른 글

| Atmega128 PWM 예제코드 (1) | 2023.02.24 |

|---|---|

| 다이오드의 종류와 특성(다이오드,쇼트키다이오드,제너다이오드) (2) | 2022.12.26 |

| 라즈베리파이 pi 로그인이 안됨 해결방법.(Bullseye 버전 이후 default ID 삭제) (0) | 2022.09.20 |

| ESP IDF 설치 (Mac OS) (1) | 2021.07.16 |

| Raspberry pi cm4 SPI0 CE0 CE1 사용 / ENC28J60, TFT 2.2 LCD 사용 (0) | 2021.06.17 |